DRAMとは?DRAMの構造・動作原理を図解で説明

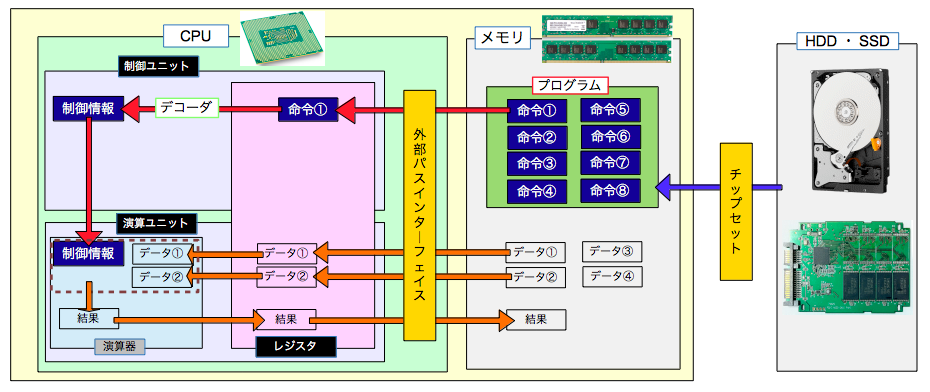

DRAMとはダイナミック・ランダム・アクセス・メモリ(Dynamic Random Access Memory:以降、DRAMと呼ぶ)の略で、コンピュータ内部の記憶装置であるメモリ(主記憶装置:以降、メモリと呼ぶ)に実装されています。

ランダム・アクセス・メモリ(Random Access Memory)の「ランダム・アクセス」とは、

- データを順番に取り出すこと(シーケンシャル・アクセス)が出来ない

- アドレスを指定すればデータを自由に取り出すことが出来る

という意味です。

シーケンシャル・アクセスの代表例としては、磁気テープ等々が挙げられます。

この記事では、DRAMの

- 基本構造

- 動作原理

それぞれについて解説していきます。

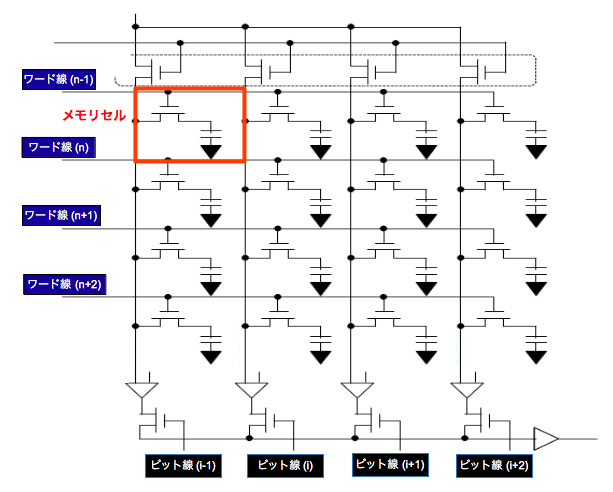

DRAMの基本構造

DRAMは半導体の技術を応用した記憶装置で、メモリセルが縦横に並んで形成されています。

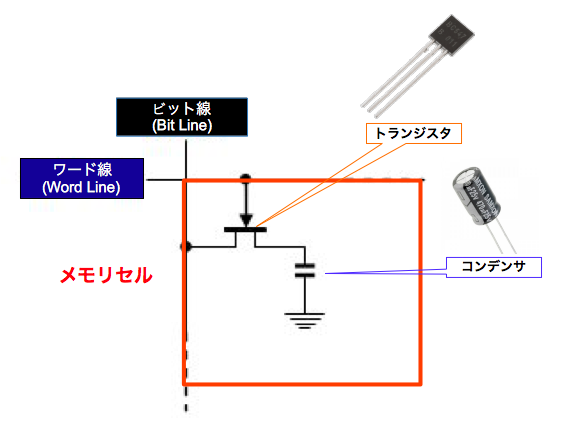

メモリセルは、

- 一つの選択トランジスタ(NMOSトランジスタ)

- 直列配置されたコンデンサ

から構成されています。

トランジスタに関する記事はこちら

コンデンサに関する記事はこちら

このメモリセル一つずつに、2進数のデータ

- 0

- 1

どちらの情報が記録されています。

2進数に関する記事はこちら

メモリセル内の2進数のデータである

- 0

- 1

の区別は、コンデンサの電荷の有無で判断しています。

トランジスタがスイッチの役割を担っており、

- スイッチをオン -> コンデンサに電荷が貯まる。ある一定値以上に電荷がたまった状態・・・1

- スイッチをオフ -> コンデンサに電荷が貯まらない・・・0

となっています。

DRAMのメモリセルは、

- ワード線(Word Line)

- ビット線(Bit Line)

が縦横に格子状に走っており、その交差点に配置されています。

DRAMの動作原理

DRAMの動作には

- 書き込み動作

- 読み出し動作

があります。

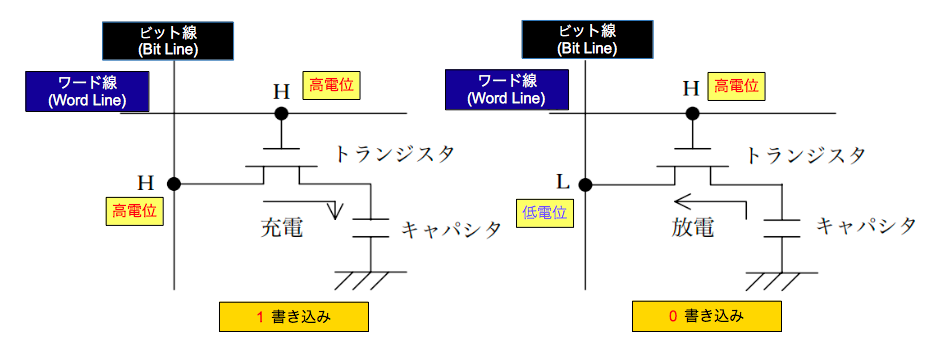

ワード線(Word Line)及びビット線(Bit Line)の

- 電位が高い時は H(High) -> 2進数の[1]を書き込む

- 電位が低い時は L(Low) -> 2進数の[0]を書き込む

基本的に、電位のHとLを制御して2進数のデータを書き込みます。

書き込み動作

メモリセルに[1]を書き込む場合・・・

- ワード線の電圧を上げた状態(電位のH)で

- ビット線の電圧を上げ

- トランジスタを通してコンデンサを充電

- 充電

- 電荷の蓄積

がされます([1]が書き込まれる)が、すでに書き込まれていれば変化はありません。

メモリセルに[0]を書き込む場合・・・

- ワード線の電圧を上げた状態で

- ビット線の電圧を0[V]にして

- トランジスタを通して蓄えられた電荷を放電

読み出し動作

メモリセルの[1]の記憶情報の読み出しの場合・・・

- ワード線の電圧を上げた状態(電位のH)にします

- ビット線に放電電流が流れ

- ビット線電位を瞬間的に上げます

- これを検出回路で検査

- [1]を判別します

メモリセルの[0]の記憶情報の読み出しの場合・・・

- [0]のメモリセルではビット線に電流が流れず

- 電位が変化しないので[0]と判別できます。

リフレッシュ

DRAMでは、コンデンサにおける蓄積電荷が微小な漏れ電流により徐々に記憶が失われます。

その為、一定の時間ごとに同一データを繰り返し書き込むリフレッシュ(refresh)という記憶の保持動作(再充電)が必要になります。

これがDRAMの「Dynamic(動的)」の名前の由来になっています。

データを保持するためには常に通電しておく必要があり、そのため

- データのアクセスの有無に関わらず電力を消費

- リフレッシュ間のデータ読み出し不可

- CPUからのアクセス待機による速度低下 等々

のリフレッシュによる弊害もあります。

以上、DRAMの

- 基本構造

- 動作原理

についての解説になります。

コメント