キャッシュメモリとは?基本構造・原理を図解で説明

「メモリ(Memory)」は、日本語で一般的に「記憶」と訳されますが、コンピュータ界での「メモリ」は、コンピュータが処理すべきデジタルデータをある期間保持する為に使用される

- 電子部品

- 電子装置

- 電子媒体

の総称を指す事になります。

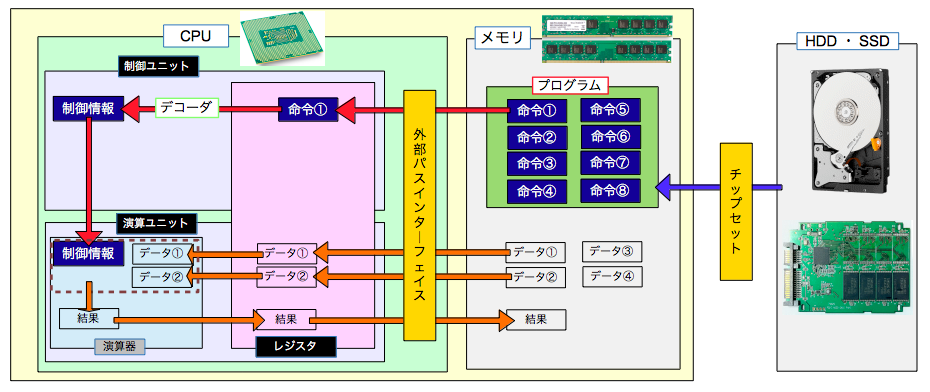

コンピュータ内部では、プログラム内の命令・データを

- 処理・実行する部分・・・CPU

- 保存・格納する部分・・・メモリ

とそれぞれ役割があり、一つのコンピュータ内部には数種類の異なる記憶装置が存在します。

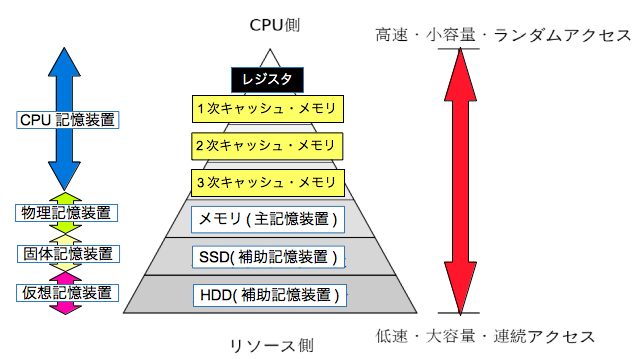

CPUの近くに位置する記憶装置ほど

- 高速な命令・データの転送

- 小容量

という特徴を持って一方で、CPUから遠くに位置する記憶装置は

- 低速な命令・データの転送

- 大容量

という特徴を持っています。

CPUやレジスタに関する記事はこちら

コンピュータは以前から

- メモリ(主記憶装置:以降、メモリと呼ぶ)

- HDD・SSD(補助記憶装置)

の記憶装置や伝送路の性能がCPUの処理装置の性能に追いつけませんでした。

ノイマン型コンピュータでは

- 記憶装置に命令を格納

- CPUが命令を実行

このプロセスは、CPUは必ず外部バスを通して記憶装置にアクセスしなければならず、CPUと記憶装置のアクセス速度が遅ければコンピュータ全体のボトルネックになっていました。

そこで、CPUがデータや命令などの情報を取得・更新する際、

- 記憶装置や外部バス等の遅延・低帯域を隠蔽

- CPUと記憶装置の性能差を埋める

これらのためにキャッシュメモリが用いられるようになりました。

- 隠し場

- 貯蔵所

という意味のCacheです。

つまり、コンピュータ界では「プログラムの命令・データ」を貯蔵しておく場所という事になります。

この記事では、CPU記憶装置の一つであるキャッシュメモリの

- 基本構成

- 基本原理

それぞれについて説明、最後に人気CPUを見ていきます。

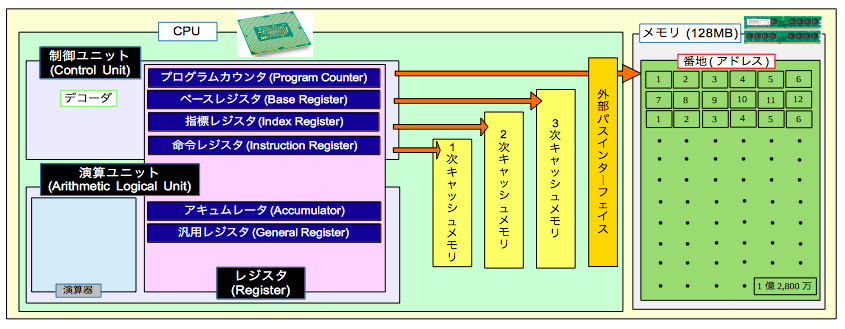

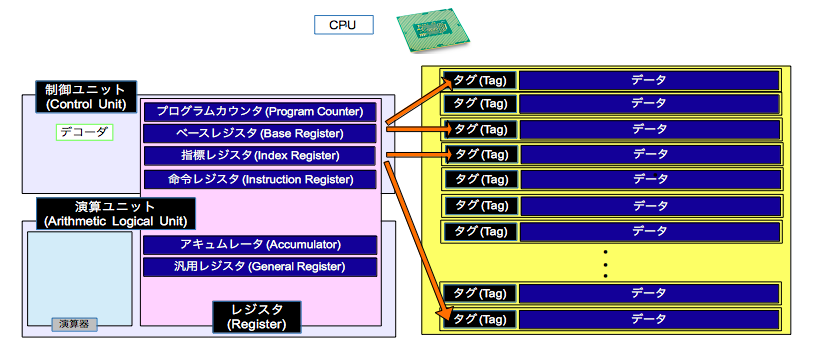

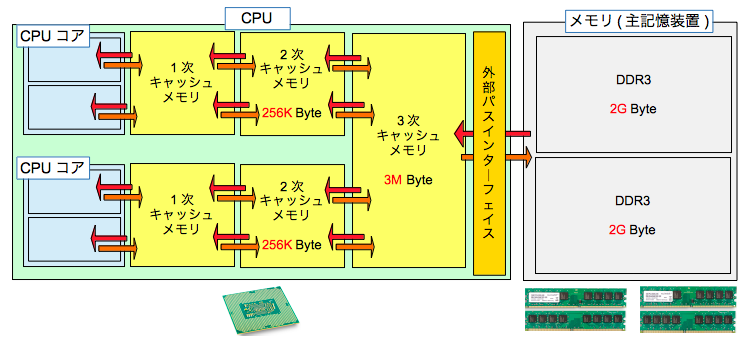

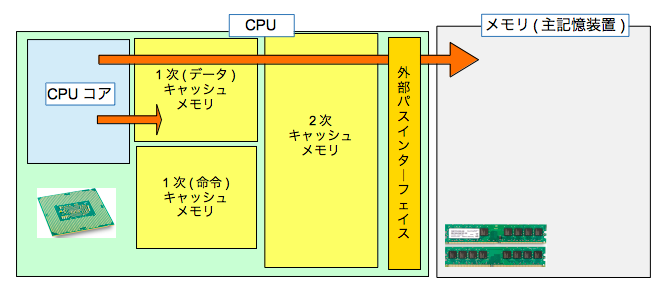

キャッシュメモリの基本構成

キャッシュメモリは記憶階層では、

- CPU(レジスタ)

- メモリ

の間に存在し、メモリの内容のごく一部を一時的に保存しておく記憶装置です。

以前はCPUチップの外部にキャッシュメモリを搭載するのが主流でしたが、半導体微細化技術の向上により、現在はCPUチップ上にキャッシュメモリを搭載しています。

キャッシュメモリは

- メモリに比べるとはるかに高速

- 記憶容量が少ない

という特徴を持っています。

キャッシュメモリは、

- CPUが頻繁にアクセスすると予想される命令・データの保存

- 低速なメモリへのアクセス頻度を最大限度まで減らす

- CPUの平均的な待ち時間を短縮すること演算性能を高める

- CPUとメモリを接続するバスのデータ転送速度に対する要求値を下げる

という役割を担っています。

キャッシュメモリは、通常は下位レベルの記憶装置である

- メモリ

- 補助記憶装置

より小容量・高速なSRAM(Static Random Access Memory)を用いて構成されます。

SRAMは、

- 半導体メモリの一種

- Static(スタティック:静的)な回路方式により情報を記憶するフリップフロップ等の順序回路

- DRAM(Dynamic Random Access Memory)とは異なり、定期的なリフレッシュ(回復動作)が不要

- 揮発性メモリ

という特徴があります。

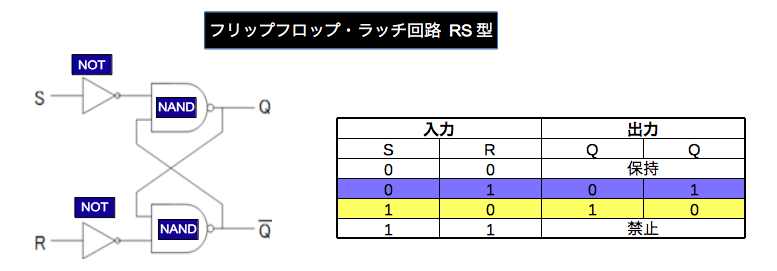

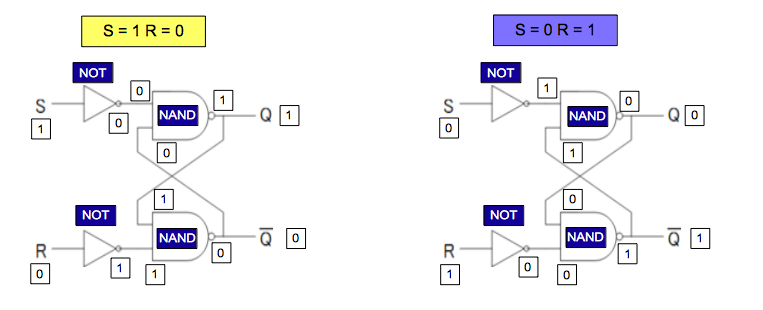

フリップフロップ回路

フリップフロップ回路(Flip-flop)とは、2進数の基本である1ビットの情報を一時的に

- 0

- 1

どちらかの状態として保持する(記憶する)ことができる論理回路です。

フリップフロップ回路はその構造と機能によって

- RS型(Reset・Set)

- JK型(語源不明)

- D型(Delayed)

- T型(Toggle)

に分類されます。

AND演算・・・入力する2つの値が

- 両方1(真) -> 演算結果が1(真)

- 片方だけ1(真) -> 演算結果が0(偽)

NAND演算・・・NOT演算とAND演算を掛けあわせた演算で、入力する値が全て1のときのみ出力する値が0

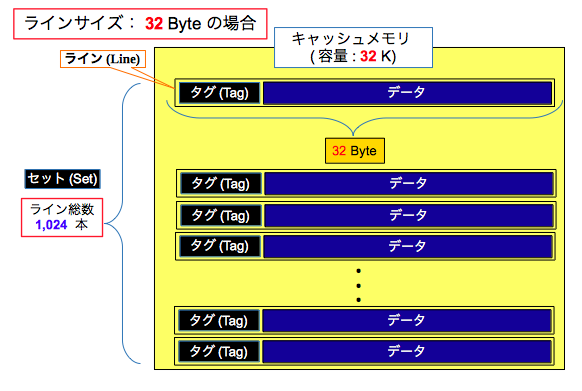

データ格納構造

キャッシュメモリに格納するデータには

- ライン(Line)・・・大きさの単位

ライン(Line)の大きさ(長さ)は、16 Byteから256 Byte位です

- タグ(Tag)・・・キャッシュメモリに格納したデータのアドレス

例えば、64 Byte のライン(Line)下位ビットのアドレス(下位6 bit)はタグ(Tag)にする意味が無く、必要な上位ビットのアドレス(上位アドレス)だけをタグ(Tag)とします

- セット(Set)・・・ライン(Line)の集まり

という単位があります。

また、キャッシュメモリにデータを格納する方式には

- フル・アソシアティブ方式

- ダイレクトマップ方式

- セット・アソシアティブ方式

があります。

フル・アソシアティブ方式(Fully Associative)

Associative(アソシアティブ)は、日本語で

- 連帯の

- 連想の

という意味です。

フル・アソシアティブ方式はCPUが要求したアドレスとキャッシュメモリのタグを全て比較する方式になります。

メリットには、キャッシュメモリとメモリのやりとりに制限がないことですが、デメリットとして

- 回路の規模が大きくなること

- 消費電力が大きくなる

が挙げられます。

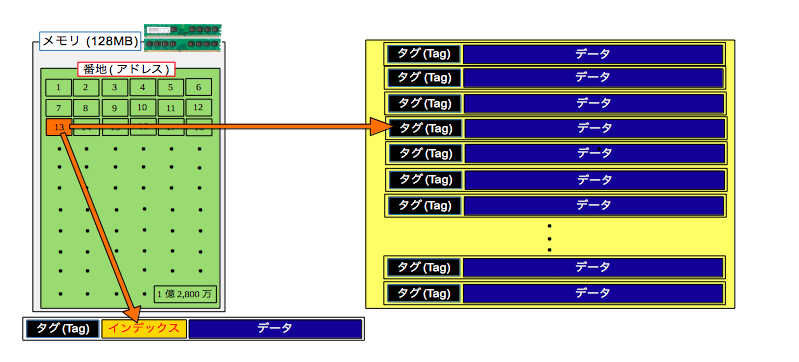

ダイレクトマップ方式(Direct Mapped)

ダイレクトマップ方式は、メモリのアドレスからキャッシュメモリのラインの位置を予め決めてしまう方式です。

具体的には、「インデックス」という、メモリのアドレスの一部(中位のアドレス)を、キャッシュメモリのラインのアドレスに割り当てます。

メリットは、「インデックス」を利用してキャッシュメモリを読みに行くという動作になるため、

- 回路規模がコンパクト

- 回路の動作を高速にしやすい

という点が挙げられる一方、デメリットとして、

- メモリで同じ「インデックス」に対応するデータは複数個存在するのに対し、キャッシュメモリで格納可能なラインが一つしかない

- 既にデータが埋まっているキャッシュメモリのラインに同じ「インデックス」のデータを格納するには前のデータを消して上書きするしかない

という点が挙げられます。

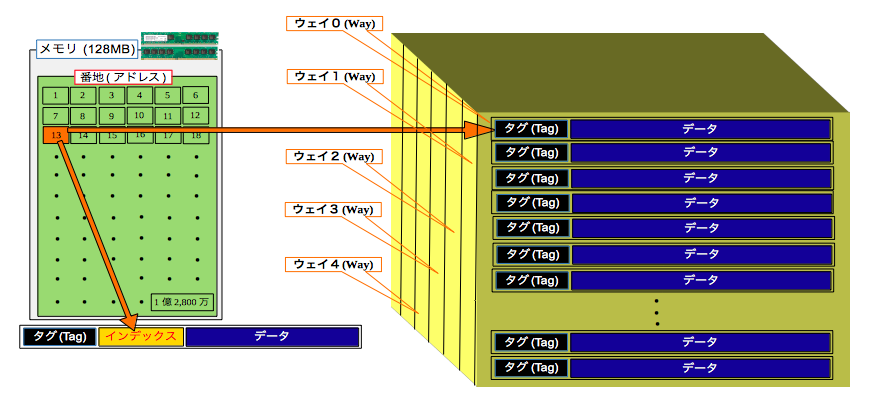

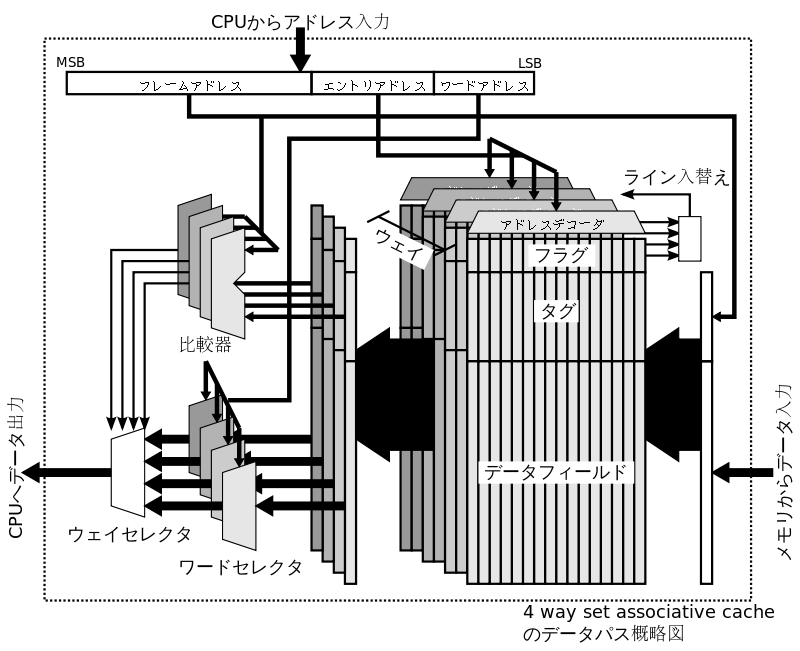

セット・アソシアティブ方式(Set Associative)

セット・アソシアティブ方式は

- フル・アソシアティブ方式

- ダイレクトマッピング方式

の中間的な方式になります。

現在、ほとんどのCPUアーキテクチャ(設計)が採用するキャッシュ構造です。

「インデックス」を利用してマッピングするという点ではダイレクトマッピング方式と変わりませんが、同じ「インデックス」に対応するキャッシュメモリのラインを複数個用意しています。

- ウエイ(Way)・・・「インデックス」に対応するキャッシュメモリのラインのグループ

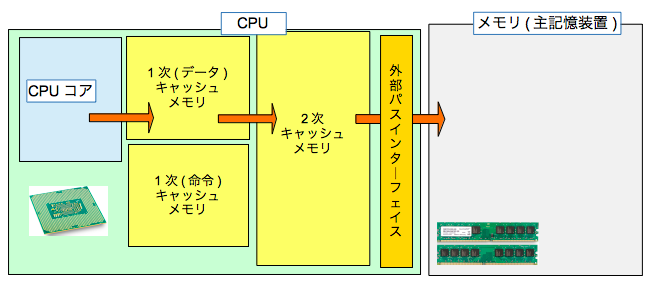

キャッシュメモリの基本原理

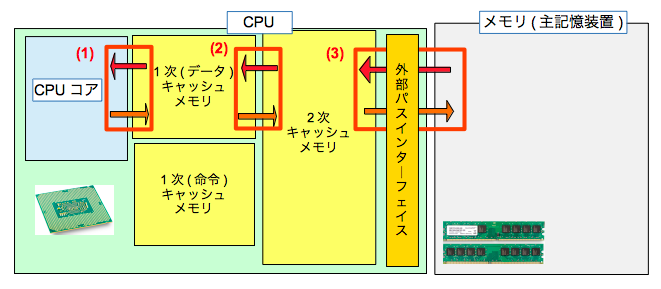

CPUがロード命令(データをレジスタに読み込み)を出した場合、下記の三パターンのアクセス方法が考えられます。

(1)1次(データ)キャッシュメモリに対応するデータが存在

- 1次(データ)キャッシュメモリにヒット

- 1次(データ)キャッシュメモリからデータを読み込み

- CPUに戻す

(2)1次(データ)キャッシュメモリには対応データが存在せず、2次キャッシュメモリに存在

- 1次(データ)キャッシュメモリはミス

- 2次キャッシュメモリはヒット

- 2次キャッシュメモリのデータを読み込み

- CPUに戻すとともに、1次1次(データ)キャッシュメモリにデータをコピー

- 1次(データ)キャッシュメモリのラインが全て埋まっていた時、コピー前にどれかのラインからデータを追い出し、空きラインを作る

(3)1次(データ)キャッシュメモリ・2次キャッシュメモリの両方に対応するデータが存在しない

- 1次(データ)キャッシュメモリはミス

- 2次キャッシュメモリもミス

- メモリからデータを読み込み

- CPUに戻すとともに、1次(データ)キャッシュメモリと2次キャッシュメモリにデータをコピー

- コピー前に、1次(データ)キャッシュメモリと2次キャッシュメモリのラインに空きラインを作っておく

キャッシュメモリ・ラインの入替アルゴリズム

キャッシュメモリには大きく分けると

- アロケーション(allocation)・・・メモリからデータをキャッシュメモリのラインにコピーする動作

- エビクション(eviction)・・・特定のキャッシュメモリのラインからデータを追い出して空きのラインを作る動作

の二つの動作が存在します。

アロケーション(allocation)・・・日本語で、- 割り当て

- 配置

エビクション(eviction)・・・日本語で、

- 立ち退き

という意味です。

アロケーション動作は、

- CPUがデータを読み込むタイミング

- CPUがデータを書き込むタイミング

で行われます。

一方、エビクション動作では、キャッシュメモリ構造がセット・アソシアティブ方式の場合、キャッシュメモリのラインからデータを立ち退かせる方法は、

- ランダム(Random)

- ラウンドロビン(Round Robin)

- LRU(Least Recently Used)

があります。

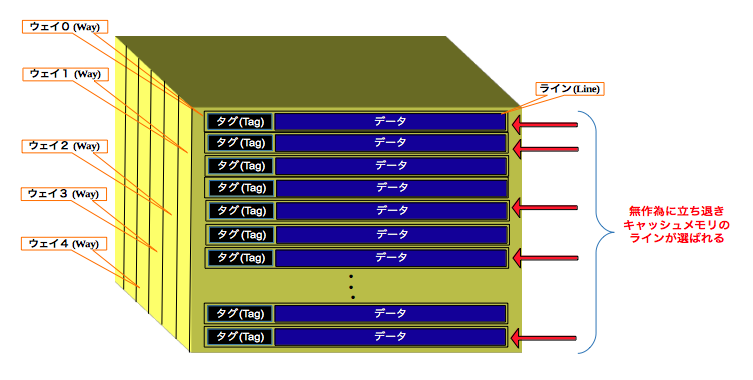

ランダム(Random)

ランダム(Random)とは、無作為に立ち退かせるデータのキャッシュメモリのラインを決める方法です。

この方式は、頻繁にアクセスするキャッシュメモリのラインのデータが消されてしまうというリスクを孕んでいます。

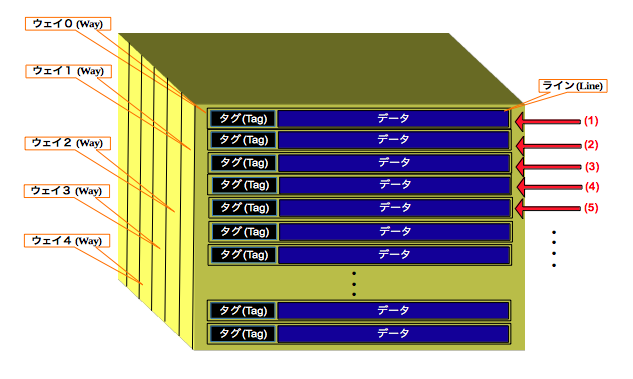

ラウンドロビン(Round Robin)

ラウンドロビン(Round Robin)とは、立ち退かせるデータのキャッシュメモリのラインを順番にずらしていく方法です。

ランダム(Random)と同様、各キャッシュメモリのラインのアクセス頻度に拘らない為、あまりヒット率が高くありません。

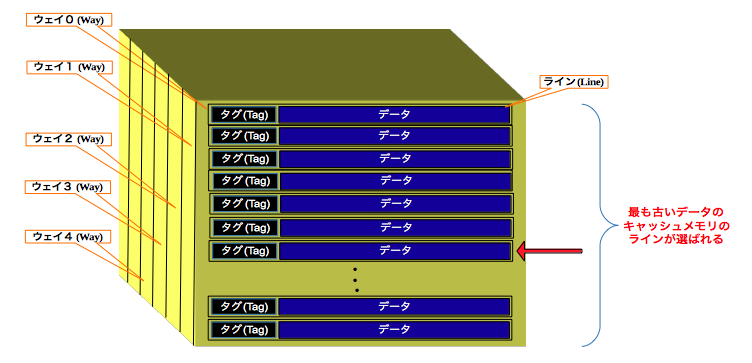

LRU(Least Recently Used)

LRU(Least Recently Used)とは、最も古くアクセスされたデータのキャッシュメモリのラインを立ち退かせる方法です。

キャッシュの読み込み・書き込み

キャッシュメモリを搭載したシステムでは、メモリのデータは基本的にキャッシュメモリを介して読み書きされます。

データの書き込みは、大きく分けて

- ライトスルー(write through)・・・キャッシュメモリとメモリに同時に書き込む方法

- ライトバック(write back)・・・キャッシュメモリだけに書き込み、メモリには後で書き込む方法

と二種類あります。

ライトスルー

ライトスルー(write through)は、必ずメモリへの書き込みを伴う為、キャッシュメモリが存在しない場合と同等にパフォーマンスが落ちる場合がありますが、メモリの内容は常に最新の状態に保たれます。

ライトバック

ライトバック(write back)は、キャッシュメモリにのみ書き込みが行われるため、高速に動作します。

メモリに書き込まれるタイミングが遅れる為、プログラムからは「メモリに書き込みを行ったが、実際には書き込まれていない」という状態が発生することになります。

人気CPU

2020年6月時点における人気CPUベスト3は

- Ryzen 5 1600 (AF)

- Ryzen 3 3300X

- Ryzen 5 3600

になります。

Ryzen 5 1600 (AF)

リンクスペック メーカー AMD プロセッサ名 Ryzen 5 1600 (AF) 世代 第2世代 ソケット形状 Socket AM4 コア数 6 クロック周波数 3.2GHz 最大動作クロック周波数 3.6 GHz スレッド数 12 マルチスレッド ○ 二次キャッシュ 3MB 三次キャッシュ 16 MB Ryzen 3 3300X

リンクスペック メーカー AMD プロセッサ名 Ryzen 3 3300X 世代 第3世代 ソケット形状 Socket AM4 コア数 4 クロック周波数 3.8GHz 最大動作クロック周波数 4.3 GHz スレッド数 8 マルチスレッド ○ 二次キャッシュ 2MB 三次キャッシュ 16 MB Ryzen 5 3600

リンクスペック メーカー AMD プロセッサ名 Ryzen 5 3600 世代 第3世代 ソケット形状 Socket AM4 コア数 6 クロック周波数 3.6GHz 最大動作クロック周波数 4.2 GHz スレッド数 12 マルチスレッド ○ 二次キャッシュ 3MB 三次キャッシュ 32MB 以上、

- キャッシュメモリの基本構成

- キャッシュメモリの基本原理

- 人気CPU

についての説明になります。

コメント